Recently, I had the opportunity to use a SPI controller from Opencores in a customer design based on an Intel PXA255 processor and a Xilinx CPLD. The customer did not want to change the processor or the CPLD family, but needed an extra SPI interface in the device. I had my doubts, but mentioned I would look into a SPI controller from Opencores. To my surprise, the core fit in a Xilinx CPLD and worked out very well. We have since upgraded to a Altera MAXII CPLD. This review details this effort.

SPI Controller Overview

The SPI controller is based on the interface for a standard Motorolla SPI controller and is available at http://www.opencores.org/projects.cgi/web/spi/overview . The core includes the following features:

- Full duplex synchronous serial data transfer

- Variable length of transfer word up to 128 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- 8 slave select lines

- Fully static synchronous design with one clock domain

- Technology independent Verilog

- Fully synthesizable

A datasheet type document is provided with the core that provides the necessary information for developers writing software for this core.

The Wishbone bus

Most of the cores from Opencores uses the Wishbone bus standard. The Wishbone bus is a synchronous bus designed to be used inside an IC. The CPLD was connected to the PXA255 processors asynchrous bus, so most of the effort required was to create an PXA255 <-> Wishbone interface module. At some point, I hope to release this module on Opencores.

Simulation

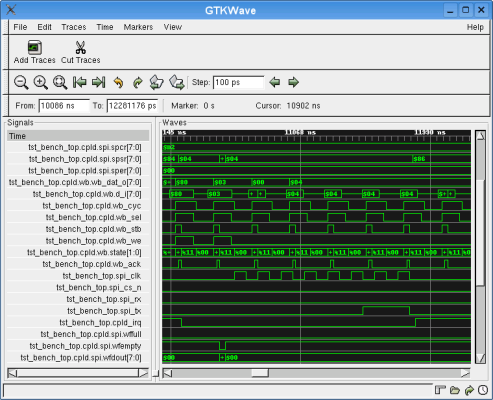

The simulation was done using the Icarus Verilog simulator under Linux. Below is a screen shot of the simulation displayed in GTKWave:

Conclusion

The Opencores SPI core worked out very well in our design and I was very impressed with quality of this core. The documentation is more than adequate. Standards like Verilog make it very easy to move designs between different vendors devices and allows designers to use tools of their choice such as the Icarus Verilog simulator. As FPGAs and CPLDs become more larger and more standand, Opencores is valuable resource for adding standard interfaces to these devices.